# **PEAKTOP Instruction Set Architecture Manual**

## PEAKTOP ISA v1.3.10.5

Rev. 210104

IHP - Innovations for High Performance Microelectronics

## Copyright notice

© IHP GmbH 2021. Verbatim copying and distribution of this document (or parts of it) is granted provided that this copyright notice is preserved on all copies.

This document is a detailed specification of the PEAKTOP Instruction Set Architecture (ISA).

#### Audience

The document is to be used by architects, system designers, hardware developers, compiler and operating system developers, software writers (especially in assembly) for systems based on the PEAKTOP ISA.

#### Version

The version of the PEAKTOP ISA is given by four numbers. The first number specifies the version regarding the general PEAKTOP philosophy and foundations such as basic architectural properties, view of registers, memory, exception and interrupt handling mechanism, etc. The second, third and fourth number specify the versions of the data transfer, arithmetic/logic and control instructions, respectively. The initial version was v1.0.0.0, and up to v1.3.10.4, the PEAKTOP ISA was in the development phase. The first public document describing the PEAKTOP ISA is for version v1.3.10.4.

#### History

The PEAKTOP ISA has its origins at the Faculty of Electrical Engineering and Information Technologies (FEEIT) – Skopje, Macedonia (www.feit.ukim.edu.mk), in the magister work of Aleksandar Simevski under the mentorship of Prof. Dr. Aristotel Tentov which started in 2007. In January 2010, the defense of the magister thesis took place in Skopje, with co-mentoring from Prof. Dr. Rolf Kraemer, also a member of the thesis committee (together with Prof. Tentov and the Dean of FEEIT at that time Prof. Dr. Mile Stankovski). Prof. Kraemer is a professor at the Brandenburgische Technische Universität (BTU) Cottbus-Senftenberg, Germany (www.b-tu.de), and a head of the System Design Department in the state research institute IHP Microelectronics (www.ihp-microelectronics.com). The cooperation between IHP and FEEIT was initiated in a project funded by Deutscher Akademischer Austauschdienst (DAAD). At that time, the PEAKTOP ISA was designed, but an implementation was lacking. Aleksandar Simevski after the defense of the magister thesis moved to Germany for obtaining the PhD degree at BTU under the mentorship of Prof. Kraemer, with a scholarship provided by the German state of Brandenburg. An 8-core multiprocessor based on the PEAKTOP ISA v1.2.5.2 was then implemented, produced and tested successfully in IHP 130 nm technology. This chip was used as a demonstrator for a dynamically-adaptable multiprocessor framework, named Waterbear which was developed in the PhD thesis.

#### Name

If one assumes that the word PEAKTOP is written in Cyrillic, he will read it as "REACTOR", which is actually the original name of the architecture, inspired from the nuclear reactor. However, virtually all of the people whose native language is written in Cyrillic assume that the word is written in English, and they like the name because it represents the "top of the peak", or "the highest peak of all". Thus, the name remained, and it can be read in both ways. Therefore, in this document it is always written with upper case letters because of the "double" meaning.

#### Style convention

CODE font is used to display code in assembly or high-level program languages, as well as names of variables, bit-fields, constants, binary values, etc.

**ADD** reg0, reg1 is an example of a valid assembly line. However, listings of program parts or code blocks in assembly or higher-level languages (incl. pseudo-languages) are given in special figure-like environment.

$<\!\!\text{replace here}\!\!>$  denotes a placeholder which should be replaced with one of at least two optional terms.

Warning blocks are used to stress specific or exceptional situations.

Information blocks are used used to display important information or additional explanation.

## Supplementary materials

PEAKTOP-related literature:

- PEAKTOP Assembler (PAS v4.3.5.5)

- PEAKTOP Multiprocessor Debugger (PMD v2.3.1.5)

- PEAKTOP DW Execution Pipeline

## Changelog

#### v1.3.10.5

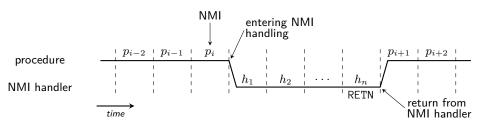

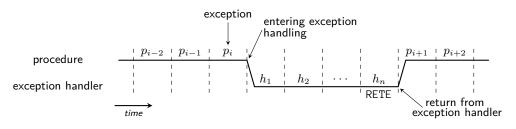

The changes of this PEAKTOP ISA version in respect to v1.3.10.4 is the introduction of additional types of the system instructions RETE and RETN (see Subsections 6.1.51 and 6.1.52). In v1.3.10.4 these instructions do not take arguments and automatically restore some of the bits of the SYSTEM CONTROL REGISTER (see Subsection 5.10) to their values before the exception or Non-Maskable Interrupt (NMI) handling, respectively.

Now the RETE and RETN instructions can also take an (optional) single argument: either a General-Purpose Register (GPR) or a 20-bit unsigned immediate value with which the entire SYSTEM CONTROL REGISTER is overwritten. This is sometimes useful in system procedures, e.g., simultaneously changing the GPR bank, enabling exceptions and returning to user mode with one instruction. Of course, the specification of RETE and RETN without arguments has remained the same and is not changed in respect to the previous version v1.3.10.4.

#### **Document changes:**

| Subsection 3.3                  | This Subsection is updated to include the description of the new types of RETE and RETN instructions.                                                                                                                                                             |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Subsections 4.1, 4.2 and 4.4    | The descriptions of the exception and NMI handling are updated with additions of the newly-added types of RETE and RETN.                                                                                                                                          |

| Subsections 6.1.49<br>to 6.1.52 | Update of the detailed instruction specification of the RET, RETI,<br>RETE and RETN group of instructions. RET and RETI are the<br>same as before (only their description is updated), while RETE<br>and RETN have new additional types which are also described. |

Tables 10, 68 and 69The tables are updated to include the new types of RETE and<br/>RETN.

Entire document Several typo corrections.

## v1.3.10.4

First public version.

## Thank you!

Thank you for using the PEAKTOP ISA and the products based on it. You are highly encouraged to send us feedback, suggestions, error reports, etc. to:

simevski@ihp-microelectronics.com

IHP - Innovations for High Performance Microelectronics

## Contents

| Pr | eface | 2      |                                                     | 3  |

|----|-------|--------|-----------------------------------------------------|----|

| Co | onten | ts     |                                                     | 7  |

| 1  | INT   | RODU   | CTION                                               | 13 |

| 2  | ARC   | сніте  | CTURAL PROPERTIES                                   | 14 |

|    | 2.1   | Machi  | ne modes                                            | 14 |

|    |       | 2.1.1  | Natural machine mode                                | 14 |

|    |       | 2.1.2  | FP machine mode                                     | 14 |

|    |       | 2.1.3  | Regularity                                          | 15 |

|    | 2.2   | Regist | er files                                            | 15 |

|    |       | 2.2.1  | Enumeration, labeling and representation            | 15 |

|    |       | 2.2.2  | Registers operating in lower machine modes          | 16 |

|    |       | 2.2.3  | Circularity                                         | 16 |

|    |       | 2.2.4  | GPR file                                            | 17 |

|    |       | 2.2.5  | Special register file                               | 18 |

|    |       | 2.2.6  | DSP, FPR and implementation-specific register files | 18 |

|    | 2.3   | Memo   | ry addressing                                       | 18 |

|    |       | 2.3.1  | Address space                                       | 18 |

|    |       | 2.3.2  | Data addressing modes                               | 19 |

|    |       | 2.3.3  | Instruction addressing                              | 19 |

|    |       | 2.3.4  | Address alignment                                   | 19 |

|    |       | 2.3.5  | Endianness                                          | 20 |

|    |       | 2.3.6  | Orthogonality                                       | 20 |

|    | 2.4   | Progra | am flow                                             | 20 |

|    |       | 2.4.1  | INSTRUCTION COUNTER                                 | 20 |

|    |       | 2.4.2  | Data and control inter-dependencies                 | 20 |

|    |       | 2.4.3  | Pausing execution                                   | 21 |

|    | 2.5   | Operat | ting system support                                 | 21 |

|    | 2.6   | Multip | processing support                                  | 21 |

| 3 | BIN | ARY L  | AYOUT                       | 23 |

|---|-----|--------|-----------------------------|----|

|   | 3.1 | Data t | ransfer instructions        | 23 |

|   |     | 3.1.1  | Memory transfer             | 24 |

|   |     | 3.1.2  | Inter-register transfer     | 25 |

|   |     | 3.1.3  | Load immediate              | 26 |

|   | 3.2 | Arithm | netic/logic instructions    | 26 |

|   |     | 3.2.1  | Integer unit                | 27 |

|   |     | 3.2.2  | Floating point unit         | 28 |

|   |     | 3.2.3  | DSP unit                    | 28 |

|   | 3.3 | Contro | l instructions              | 29 |

|   |     | 3.3.1  | Program transfer            | 29 |

|   |     | 3.3.2  | Return from routine         | 30 |

|   |     | 3.3.3  | Pause instruction execution | 31 |

|   | 3.4 | Summ   | ary                         | 31 |

| 4 | EVC | EDTIC  | INS AND INTERRUPTS          | 35 |

| 4 | 4.1 |        | Iaskable Interrupt (NMI)    | 35 |

|   | 4.1 |        |                             | 36 |

|   | 7.2 | 4.2.1  | DEBUG MODE EXCEPTION        | 38 |

|   |     | 4.2.2  | INVALID INSTRUCTION         | 39 |

|   |     | 4.2.3  | SYSTEM INSTRUCTION          | 39 |

|   |     | 4.2.4  | UNIMPLEMENTED GPR BANK      | 39 |

|   |     | 4.2.5  | UNIMPLEMENTED INSTRUCTION   | 39 |

|   |     | 4.2.6  | UNIMPLEMENTED REGISTER      | 40 |

|   |     | 4.2.7  | INVALID OPERATION           | 40 |

|   |     | 4.2.8  | DIVISION BY ZERO            | 40 |

|   |     | 4.2.9  |                             | 41 |

|   |     |        | FP INVALID OPERATION        | 41 |

|   |     |        | FP DENORMALIZED OPERAND     |    |

|   |     |        | FP DIVISION BY ZERO         |    |

|   |     |        | FP OVERFLOW                 |    |

|   |     |        | FP UNDERFLOW                |    |

|   |     |        | FP INEXACT RESULT           |    |

|   |     |        | DSP EXCEPTION Ø             |    |

|   |     |        | DSP EXCEPTION 1             |    |

|   |     |        | DSP EXCEPTION 2             | 44 |

|   |     | 4.2.19 | DSP EXCEPTION 3             | 44 |

|   |     | 4.2.20 | I SYSTEM BUS ERROR          | 44 |

|   |     |        | D SYSTEM BUS ERROR          |    |

|   | 4.3              | Interru | pts                          | 45         |

|---|------------------|---------|------------------------------|------------|

|   | 4.4              | Handli  | ng mechanism                 | 46         |

|   |                  | 4.4.1   | Hierarchy and priority       | 46         |

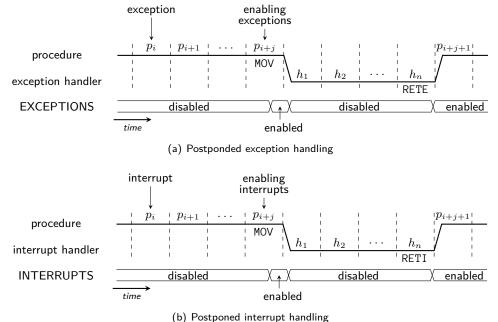

|   |                  | 4.4.2   | Postponed handling           | 47         |

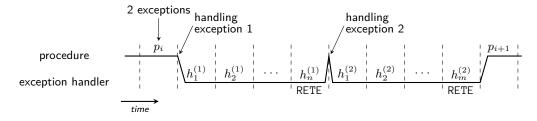

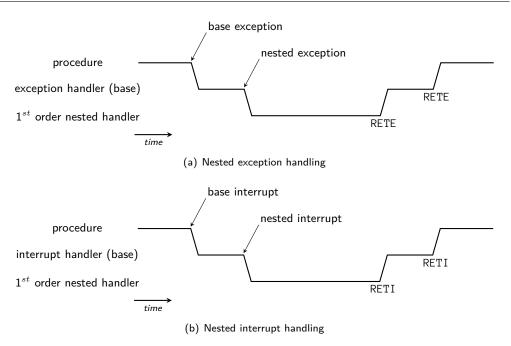

|   |                  | 4.4.3   | Nesting                      | 48         |

| - | 005              |         |                              | <b>F</b> 0 |

| 5 | -                |         |                              | 50         |

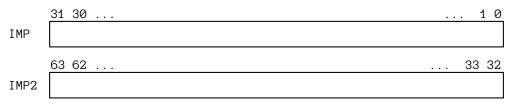

|   | 5.1              |         | MENTATION REGISTER           | 51         |

|   | 5.2              |         | TION STATUS                  |            |

|   | 5.3              |         |                              | 53         |

|   | 5.4              |         | TION REGISTER                |            |

|   | 5.5              |         | TION MASKS                   | 54         |

|   | 5.6              |         | TION TABLE BASE ADDRESS      | 54         |

|   | 5.7              |         | RUPT TABLE BASE ADDRESS      | 55         |

|   | 5.8              |         | ID                           | 55         |

|   | 5.9              |         | SS ID                        | 55         |

|   |                  |         | M CONTROL REGISTER           | 56         |

|   |                  |         | ETURN POINTER                | 56         |

|   |                  |         | TION RETURN POINTER          |            |

|   |                  |         | CONTROL REGISTER             |            |

|   |                  |         | RETURN POINTER               | 58         |

|   |                  |         | RUPT RETURN POINTER          |            |

|   | 5.16             | DSP C   | ONFIGURATION REGISTER        | 58         |

| 6 | INS <sup>-</sup> | TRUCT   | ΓΙΟΝ SET                     | 59         |

|   | 6.1              | Detaile | ed instruction specification | 59         |

|   |                  | 6.1.1   | MOV – Move data              | 60         |

|   |                  | 6.1.2   | ADD – Add                    | 66         |

|   |                  | 6.1.3   | SUB – Subtract               | 69         |

|   |                  | 6.1.4   | MUL – Multiply               | 72         |

|   |                  | 6.1.5   | DIV – Divide                 | 75         |

|   |                  | 6.1.6   | SL – Shift left              | 79         |

|   |                  | 6.1.7   | SR – Shift right             | 82         |

|   |                  | 6.1.8   | RL – Rotate left             | 85         |

|   |                  | 6.1.9   | RR – Rotate right            | 88         |

|   |                  |         | AND – AND bitwise            | 91         |

|   |                  |         | NAND – Negated AND bitwise   | 94         |

|   |                  |         | OR – OR bitwise              | 97         |

|   |                  |         | XOR – Exclusive OR bitwise   |            |

|   |                  |         |                              |            |

| 6.1.14 | SB – Set bit $\ldots$ $\ldots$ $\ldots$ 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1.15 | RB - Reset bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.1.16 | TB – Test bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.1.17 | RVB – Reverse bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.1.18 | FADD - FP Add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.1.19 | FSUB – FP Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.1.20 | $FMUL - FP \ Multiply \ \ldots \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.1.21 | $FDIV-FP\ Divide\ \ldots\ \ldots\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.1.22 | $FREM-FP\ Remainder\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.1.23 | FCMP – FP Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.1.24 | FSQR – FP Square root                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.1.25 | FABS – FP Absolute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.1.26 | FNEG - FP Negate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.1.27 | $FRND-FP$ Round to integer $\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\$ |

| 6.1.28 | FF2I - FP to integer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.1.29 | FI2F – Integer to FP $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.1.30 | $FEXT-Extend\ FP\ format\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.1.31 | $FSQZ-Squeeze\ FP\ format\ \ldots\ \ldots\ \ldots\ \ldots\ \ldots\ \ldots\ \ldots\ \ldots\ \ldots\ 141$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.1.32 | $MAD-Multiply-add  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.1.33 | $MSU-Multiply-subtract \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.1.34 | $FMAD-FP\ Multiply-add\ \ \ldots\ 149$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.1.35 | $FMSU-FP\ Multiply-subtract\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.1.36 | JMP – Jump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.1.37 | BZ – Branch if Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.1.38 | BNZ – Branch if Not Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.1.39 | BM – Branch if MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.1.40 | BMZ – Branch if MSB or Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.1.41 | BNM – Branch if Not MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.1.42 | BNMO – Branch if Not MSB or all Ones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

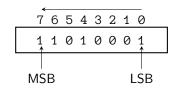

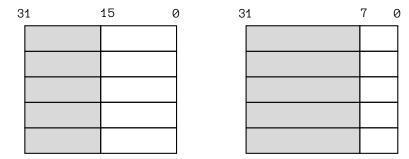

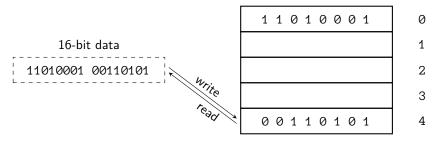

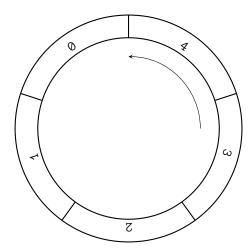

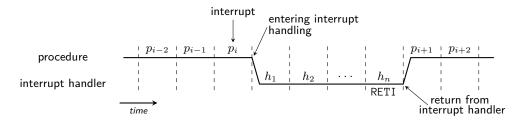

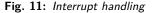

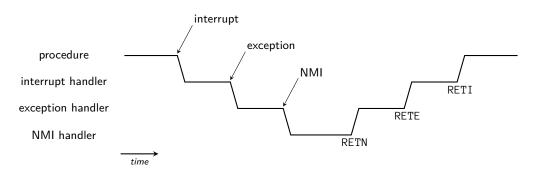

| 6.1.43 | BL – Branch if LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |