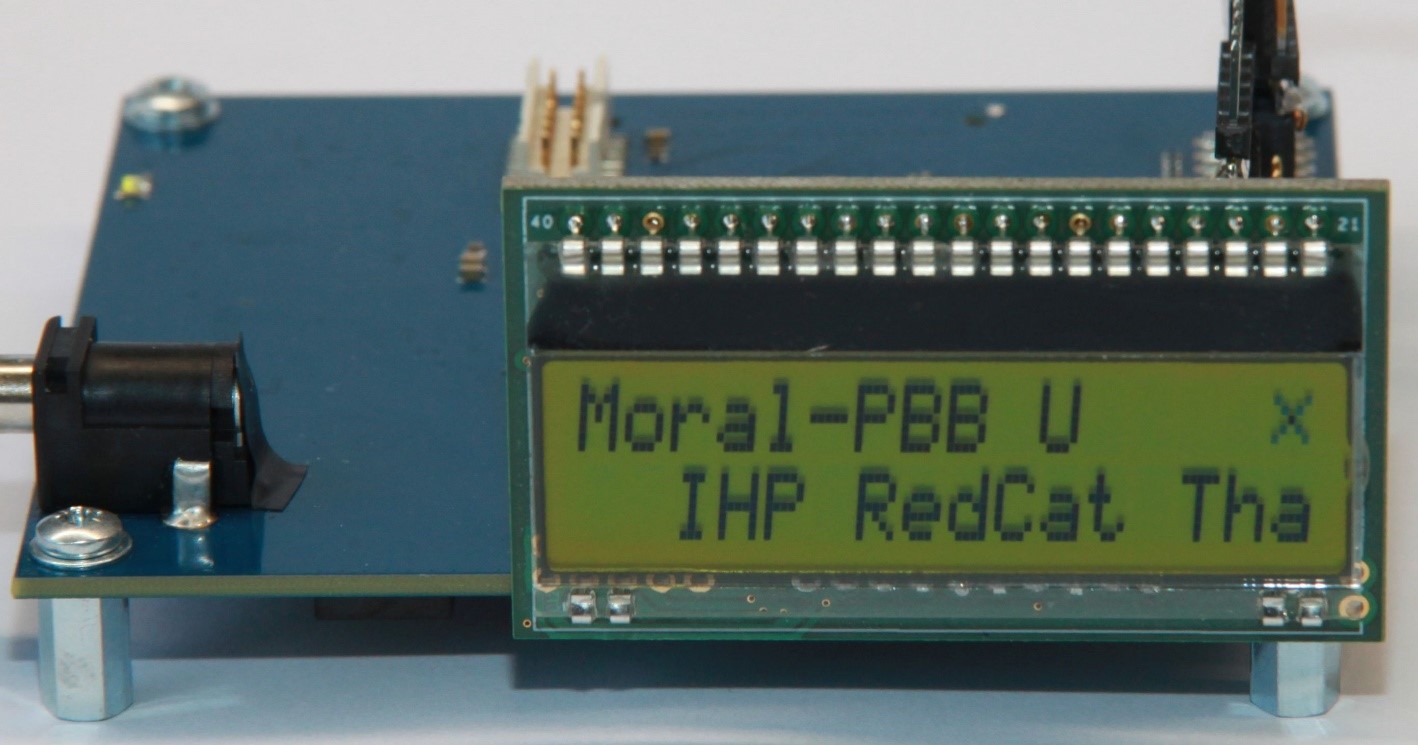

Evaluation board

The digital components in the MORAL SoC have generally been designed in some Hardware Description Language (HDL), in MORAL mostly SystemVerilog or VHDL. The source code is portable to many digital design technologies, e.g. FPGA or IHP’s 0.13 um CMOS technology, which is used for the MORAL ASIC. The first comprehensive verification is typically done by an RTL-level simulation. This is completely technology-independent and allows functional verification (but not with respect to timing) for any potential ASIC or FPGA technology.

In order to be able to do early experiments with hardware, a MORAL implementation on a programmable hardware platform, an FPGA, was developed. This allows early tests of complex software (e.g. operating system, compiler and assembler tool-chain, simple applications), which would be hardly possible in an HDL simulation due to long simulation times. A second major opportunity of the FPGA platform is the fact that it allows for easy bug fixes. If a hardware bug is detected, the repaired design can be again programmed to the FPGA platform. Then the success of the bug fix can be evaluated.

One additional opportunity of the FPGA platform is for project dissemination. Sice the MORAL microcontroller is based on the PEAKTOP Instruction Set Architecture (ISA), a new processor architecture, it is important that academia have the opportunity to know and experiment with the new architecture.

|

If you would like to have access to an evaluation board with MORAL's microcontroller, please contact us using the contact form. |